ПРЕОБРАЗОВАТЕЛИ АНАЛОГОВОЙ ВЕЛИЧИНЫ В ЧАСТОТУ ИМПУЛЬСОВ

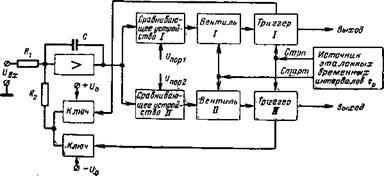

Двухканальный вариант преобразователя (Л. 39], в котором стабильная вольт-секундная площадь импульса обратной связи формируется с помощью ключевой схемы, пропускающей на вход преобразователя стабильное напряжение Uо или ток /0 в течение времени to, определяемого источником эталонных временных интервалов, т. е. генератором, стабилизированным кварцем, показана на рис. 31.

Устройство работает следующим образом. Проинтегрированное входное напряжение поступает на узлы сравнения I и //, имеющие

(Шнойолярные пороговые уровни Uпор - Когда выходное напряжение интегратора превысит пороговый уровень одного из узлов сравнения, последний срабатывает, открывая соответствующий вентиль (в качестве узлов сравнения используются устройства, например, типа триггера Шмидта). Импульс начала стабильного интервала (старт), сформированный в источнике to проходит через открытый вентиль, перебрасывая триггер в состояние, при котором сигналом с его выхода открывается ключ, через который на вход интегратора подается стабильное напряжение U0} уменьшающее уровень входного напря-

|

Рис. 31. |

жения. Импульс, соответствующий концу интервала to, возвращает триггер в исходное состояние, отключая источник стабильного напряжения от входа преобразователя.

Таким образом, стабильность вольт-секундной площади импульса обратной связи определяется стабильностью источника U0, погрешностью ключа, коммутирующего стабильный источник, а также стабильностью длительности импульса tQ.

Выбор типа ключа имеет важное значение, так как в отличие от ранее рассмотренных преобразователей изменение параметров ключа в данном типе преобразователя приводит не только к изменению наклона вольт-герцевой характеристики преобразования, но и к смещению нуля характеристики из-за гальванической связи между источником стабильного напряжения V0 и входом интегратора через ключ. Применение компенсированного ключа на транзисторах позволяет значительно уменьшить погрешности, возникающие в этом случае. По принципу включения транзисторов компенсированные ключи разделяют на [Л. 40] компенсированные ключи с последовательным включением транзисторов и компенсированные ключи с параллельным включением транзисторов.

Имеет смысл при рассмотрении работы ключа в преобразователях аналоговой величины в частоту разделить их на устройства с последовательными и параллельными ключами, коммутирующими источник стабильного напряжения.

Из компенсированных транзисторных ключей наибольшее распространение получила схема с последовательным включением транзисторов, так как она использует для коммутации обоих транзисторов одну только обмотку и позволяет коммутировать значительно большие напряжения по сравнению со схемой компенсированного ключа с параллельным включением транзисторов.

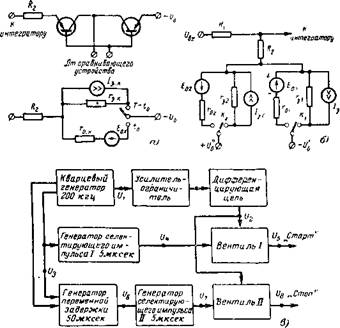

На рис. 32,а показана принципиальная и эквивалентная схемы части узла обратной связи, использующего компенсированный ключ с последовательным инверсным включением транзисторов.

На рис. 32,6 представлена эквивалентная схема преобразователя знакопеременного входного сигнала с узлами обратной связи, формирующими положительный и отрицательный импульсы обратной

|

|

связи, б каждом узле для коммутации стабильного источника используется компенсированный ключ с последовательным включением транзисторов.

Работа устройства в случае преобразования, например положительного входного напряжения, описывается уравнением

■Ущ - Т + /р2Г - /а<0 - /р. (Т - *.) = О,

где /р2Г—заряд, поступивший на івход интегратора через /32 и гз2 при разомкнутом состоянии ключа КУ, /Рі(7"—^о)—заряд, поступивший на вход интегратора через /Зі и г31 при разомкнутом ключе Ки остальные величины те же, что и в одноканальном варианте. В этом случае выражение для выходной частоты принимает следующий вид

Смещение нуля преобразователя в результате гальванической связи источника U0 и входа интегратора в этом случае определяется выражением

o — Ri 32 — ^зі) “Ь “^2 зі — 32^ ’

где

Г ъ —Г ъ = Г £/'0 = £/"0 = £/<>.

Таким образом, в двухканальном преобразователе из-за взаимной компенсации изменения параметров разомкнутого состояния ключей их влияние на общую погрешность преобразователя ослабляется.

Увеличение крутизны характеристики вход — выход преобразователя связано с усилением влияния динамических параметров ключей на общую погрешность преобразователя. Динамическими параметрами транзистора [Л. 37], работающего в ключевом режиме, является время включения, задержка и время выключения, объясняемые инерционными свойствами и в первую очередь большим временем жизни неосновных носителей в базовой области транзистора.

Возникновение временной задержки между моментом приложения управляющего сигнала и появлением установившегося значения выходного сигнала, экспоненциальный характер процесса нарастания и затем спада коммутируемого эталонного напряжения U0 приводят к зависимости величины компенсирующего заряда, поступающего на вход интегратора, от эффективного времени жизни неосновных носителей в области базы, а также коэффициента передачи базы по току (З и отношения управляющих токов базы в режиме включения и выключения транзистора и в конечном счете ограничивает максимально достижимую выходную частоту преобразователя.

Стабильность импульса to определяется в основном стабильностью импульсов старт и стоп и погрешностями, вносимыми запаздыванием в срабатывании триггеров, синхронизированных импульсами старт и стоп, и ключей, управляемых триггерами.

Блок-схема узла, вырабатывающего импульсы старт и стоп, соответствующие началу и концу временного интервала t0, показана на рис. 32,в, диаграмма напряжений в различных точках схемы — на рис. 32,г. Устройство работает следующим образом. Синусоидальное напряжение i£7i, например частотой 200 кгц с выхода кварцевого генератора, усиливается, ограничивается и после дифференцирования (U2) поступает на вентили, управляемые сигналами генераторов селектирующих импульсов (ІЛ и Ui). Импульс, выделяющий сигнал начала интервала (старт), формируется генератором селектирующего импульса / (например, ждущим мультивибратором), который запускается задним фронтом импульсов прямоугольной формы частотой 2 кгц, получаемого от кварцевого генератора после делителя. На вентиль / поступает селекторный импульс длительностью 5 мксек

Импульс, выделяющий сигнал конца интервала tо стоп, формируется аналогичным генератором импульса //, который запускается выходным сигналом генератора переменной задержки, генерирующего импульс длительностью 50 мксек. Генератор переменной задержки синхронизируется напряжением 20 кгц с делителя частоты.

Через вентили / и II на коммутирующие триггеры преобразователя поступают импульсы, имеющие очень высокую стабильность, определяемую стабильностью кварцевого генератора.

В общем случае следует учитывать стабильность частоты кварцевого генератора и погрешность от запаздывания переключения коммутирующего триггера и ключа преобразователя.

Однако полоса пропускания усилителя интегратора не может быть бесконечно широкой и для данной реальной полосы с увеличением частоты повторения импульсов, поступающих на компенсирующий вход интегратора, точность измерения уменьшается примерно пропорционально квадрату частоты. Другим неприятным явлением при повышении частоты повторения импульсов является появление дополнительных фазовых сдвигов (особенно в транзисторных усилителях в первую очередь из-за диффузионного запаздывания). Это приводит к временной задержке между входным и выходным сигналами усилителя, и в частном случае к потере устойчивости. По той же причине должен быть ограничен коэффициент усиления усилителя.

Временная задержка, также приводящая к нелинейности, возникает и вследствие того, что реальный компенсирующий импульсный сигнал не может иметь передний фронт, крутизна которого бесконечно велика.

Увеличению частоты повторения импульсов препятствует и возрастание ошибок в сравнивающем устройстве и технические трудности выполнения счетно-импульсной части преобразователя на высоких частотах заполняющих импульсов.

Повышение требования к формирователю импульсов обратной связи, к сравнивающему устройству, к интегратору приводит к необходимости существенного усложнения всего преобразователя, тщательности выполнения его узлов, введения дополнительных регулировок и настроек.

Другим путем повышения точности преобразования являются структурные методы, связанные с введением в устройство аппаратурной избыточности. В этом случае удается в значительной мере снизить требования к входящим в преобразователь узлам и к точности их регулировки и настройки. Выигрыш достигается в результате увеличения состава оборудования кодирующего устройства и введения дополнительных тактов кодирования. Полученная введением такой избыточности новая структурная схема обусловливается конкретными задачами, решением которых она служит. Поэтому имеет смысл рассматривать вопрос об общем повышении точности с точки зрения тех конкретных частных задач, с которыми приходится сталкиваться п*ри разработке преобразователей аналог — частота — код.

Как было показано, одной из составляющих погрешности преобразователя аналоговой величины в частотно-импульсный выходной сигнал является погрешность, возникающая из-за наличия к концу интервала измерения на интегрирующем конденсаторе некомпенсированного остаточного заряда Aq. Величина этого заряда в общем случае зависит от крутизны статической характеристики преобразователя и при ее достаточно большой величине будет пренебрежимо малой.

Однако следует отметить, что с ростом выходной частоты преобразователя аналог — частота усложняется и затрудняется обеспечение линейности его характеристики преобразования.

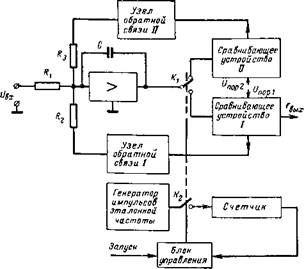

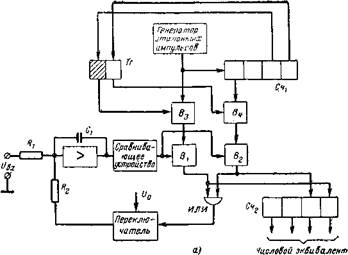

На рис. 33 представлена блок-схема преобразователя «аналог — цифра», позволяющего, не увеличивая выходную частоту и используя низкочастотные полупроводниковые приборы в основных схемах устройства, повысить разрешающую способность преобразователя [JI. 41]. Работа преобразователя происходит в два такта. В первом производится преобразование напряжения в частоту импульсов

и подсчет их счетчиком за интервал измерения Гизм, во втором такте остаточный заряд на интегрирующем конденсаторе к моменту окончания Гизм компенсируется уменьшенными по сравнению с первым тактом единичными зарядами, количество которых учитывается в счетчике как поправка.

Устройство содержит интегратор, в качестве которого используется усилитель, охваченный емкостной обратной связью, два узла сравнения, один из которых имеет пороговый уровень, равный £/порі = £/пор, а другой—£/пор2=0, вентили, узлы формирования единичных зарядов q'o и q"о, генератор тактовых импульсов, блок управления.

Работает преобразователь следующим образом. В момент начала измерения замыкается ключ /Сі и размыкается ключ /С2. В процессе интегрирования входного напряжения UBX узел сравнения I с пороговым уровнем (/порі срабатывает, отмечая момент достижения выходным напряжением интегратора порогового уровня. Импульсы с выхода узла сравнения через открытый сигналом с блока управления вентиль Ві запускают узел формирования дискретного заряда q'o. Уровень напряжения на входе интегратора уменьшается. Кроме того, импульсы с узла сравнения / через вентиль В, поступают на старшие разряды счетчика.

Через время Тизм сигнал с блока управления отключает интегратор от входного напряжения (ключ Кч размыкается) и закрывает вентиль В. Начинается второй такт преобразования. Сигналом с блока управления открывается вентиль £2 и тактовые импульсы через В2 запускают узел формирования дискретных зарядов //, формирующий заряды q"o = q'olQQ, величина которых кратна основанию системы кодирования (двоичной, десятичной и т. д.) данного типа преобразователя (в данном случае десятичной).

Остаточный нескомпенсированный заряд на интегрирующем конденсаторе уменьшается до тех пор, пока выходное напряжение интегратора не достигнет порогового уровня схемы сравнения IIUіiop2 = 0. Импульс с выхода схемы сравнения II через блок управления отключает с помощью вентиля В2 генератор тактовых импульсов. На этом процесс измерения входного напряжения заканчивается. Количество тактовых импульсов, посылаемых в формирователь II, регистрируется в младших разрядах счетчика.

Как видно, наличие второго такта приводит к увеличению времени одного цикла преобразования, причем из-за разного в каждом цикле остаточного заряда, зависящего от преобразуемой аналоговой величины, эти циклы также будут разными. Наличие специального генератора тактовых импульсов, дополнительного сравнивающего устройства и входного ключа Ki усложняет преобразователь.

Как было показано, одной из составляющих погрешности преобразования аналоговой величины в частотно-импульсный выходной сигнал является погрешность квантования, связанная с начальными условиями интегрирования

Увеличением крутизны статической характеристики преобразователя она может быть практически устранена, однако с ростом выходной частоты устройство усложняется, а его линейность уменьшается.

Введением дополнительного сравнивающего устройства, поддерживающего строго определенные постоянные начальные условия, в работающем преобразователе удается в значительной мере уменьшить эту составляющую погрешности квантования без увеличения крутизны преобразования.

Блок-схема устройства ([Л. 55] представлена на рис. 34,а. Устройство содержит дополнительно узел сравнения //, пороговый уровень которого выбран равным, например, 55% от величины £/Порі— U (рис. 34,6) основного сравнивающего устройства /, и узел обратной связи //, формирующий импульс обратной связи, несущий заряд q = q0/m, где q0 — заряд, формируемый основным узлом обратной связи /, /77 = const, т> 1. Генератор импульсов эталонной частоты со счетчиком определяют интервал измерения.

В промежутке между двумя измерениями ключом Ki к выходу интегратора подключается сравнивающее устройство II. Это приводит к тому, что в этом режиме проинтегрированное входное напряжение сравнивается с пороговым уровнем узла сравнения //ив момент его совпадения на вход интегратора из узла обратной связи II поступает компенсирующий импульс. Последний уменьшает выходное напряжение интегратора. Однако из-за присутствия аналоговой величины на входе интегратора его выходное напряжение снова возрастает и опять заставляет срабатывать узел сравнения и т. д.

Таким образом, преобразователь чв промежутке между двумя измерениями находится в непрерывном релаксационном режиме, характеризующемся тем, что постоянная составляющая выходного напряжения интегратора

а амплитуда изменения этого напряжения определяется порогом срабатывания сравнивающего устройства II. Этим самым фиксируется Начальный уровень входного напряжения йнтегратора к началу каждого нового измерения, а следовательно, исключается погрешность квантования из-за неоптимальных начальных условий интегрирования.

|

|

|

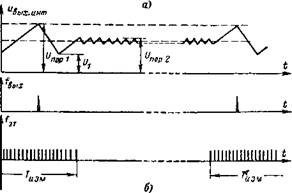

Рис. 34. Аналого-цифровой преобразователь. а — блок-схема; б — временные диаграммы работы. |

Следует отметить, что сравнивающее устройство // и узел обратной связи II могут быть простейшими, так как их погрешности мало сказываются на погрешностях устройства в целом. В частности, в качестве импульсов обратной связи в этом случае используются непосредственно импульсы, генерируемые сравнивающим устройством II в момент срабатывания последнего.

В режиме измерения ключом Ki к выходу интегратора подключается сравнивающее устройство /. В этом режиме работа устройства ничем не отличается от работы описанных ранее преобразователей аналоговой величины в частоту следования импульсов.

Несколько по иному решена та же задача в [Л. 56]. Здесь уменьшение вольт-секундной площади импульсов обратной связи и повышение частоты их повторения производится в течение последней части основного интервала измерения ГИзм. При этом, естественно, точность измерения в этой части интервала уменьшается.

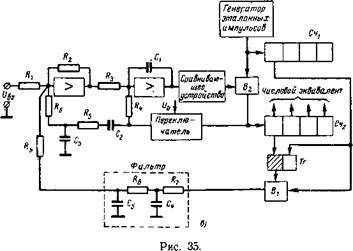

Работает устройство (рис. 35,а) в двух режимах, управляемых триггером Тг. В процессе интегрирования входного напряжения срабатывает сравнивающее устройство, отмечая момент достижения выходным напряжением интегратора порогового уровня. При этом на оба вентиля Bi и В2 подается разрешающий сигнал. Однако счетные импульсы от генератора эталонных импульсов будут проходить только через вентиль Я2, так как в данный момент сигналом от управляющего триггера Тг открыт вентиль В4. Частота следования этих импульсов

где /эт — частота следования импульсов генератора эталонной частоты; k — коэффициент деления.

Поступление счетных импульсов на счетчик Сч2 будет определяться частотой срабатывания сравнивающего устройства, которая в свою очередь пропорциональна преобразуемому аналоговому сигналу.

Каждый счетный импульс заставляет срабатывать переключатель, с помощью которого из эталонного постоянного напряжения формируются импульсы обратной связи, поступающие затем на вход интегратора. Кроме того, счетные импульсы поступают на старшие разряды счетчика Сч2.

Счетчик Счі производит отсчет интервала измерения Ги зм, и когда число импульсов в нем достигает определенной величины, близкой к числу, эквивалентному интервалу измерения, сигнал с выхода данного разряда счетчика переключает триггер в состояние, при котором закрывается вентиль £4 и открывается Вз. Счетные импульсы поступают теперь непосредственно через вентили Вз и Bi на переключатель, частота срабатывания которого становится в k раз больше. Величина заряда в k раз уменьшается, однако, счетные импульсы теперь поступают на младшие разряды преобразователя.

Импульс переполнения счетчика Счі возвращает триггер Тг и счетчики Счі и Сч2 в исходное состояние. Цикл преобразования закончен.

В данном случае разрешающая способность устройства, т. е. интервал между двумя соседними дискретными уровнями, определяется как отношение наименьшей длительности импульса обратной связи к полному интервалу измерения. Следовательно, уменьшением длительности импульса обратной связи в к раз в конце интервала измерения при соответствующем увеличении частоты срабатывания сравнивающего устройства удается в такое же количество раз увеличить разрешающую способность преобразователя, правда при некотором понижении точности преобразования.

В то же время, если сравнить данный преобразователь с устройством, имеющим стандартную структуру, то при одинаковой разре-

|

|

|

|

|

|

тающей способности последний в силу отмененных ранее обстоятельств будет иметь худшую точность. Работа преобразователя в двух режимах, когда в первом режиме частота коммутации узла обратной связи в k раз меньше, чем в стандартном преобразователе, позволяет за счет этого повысить его точность, ибо на низкой частоте меньше сказываются временные задержки в переключателе, интеграторе и сравнивающем устройстве.

Естественно, что крутизна характеристики преобразования может изменяться не только путем управления длительностью импульса обратной связи, но и воздействием на любой другой параметр, влияющий на крутизну характеристики. Каким именно параметром управлять, определяется в каждом конкретном случае структурой проектируемого преобразователя.

Другим важным фактором повышения точности преобразования является улучшение линейности характеристики «вход—выход» преобразователя, причем, как видно, линейность и разрешающая способность являются взаимосвязанными характеристиками: увеличение разрешающей способности приводит к ухудшению линейности преобразования и наоборот.

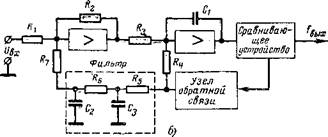

В некоторой мере отмеченные трудности могут быть устранен^ введением дополнительной отрицательной обратной связи с выхода на вход преобразователя, содержащей инерционное звено с высокой степенью сглаживания импульсных сигналов. Устройство (рис. 35,6) содержит последовательно соединенные операционный неинтегрирующий усилитель, имеющий большой коэффициент усиления и служащий для усиления входного сигнала, и интегрирующий усилитель с малым коэффициентом усиления (один каскад) и большой полосой пропускания, на вход которого поступают компенсирующие импульсы, формируемые узлом обратной связи. Дополнительная отрицательная обратная связь с инерционным звеном соединена со входом неинтегрирующего усилителя.

В такой конструкции интегратор может иметь большой дрейф нуля и плохую линейность из-за малого коэффициента усиления, но широкую полосу пропускания. Дополнительная обратная связь стабилизирует работу преобразователя и повышает линейность его характеристики «вход — выход». При этом быстродействие и достаточная разрешающая способность могут быть получены простым увеличением частоты повторения импульсов, поступающих на интегратор. Линеаризирующий сигнал обратной связи может быть получен как сглаживанием импульсов обратной связи, так и делением частоты повторения этих импульсов (рис. 35,в).

В этом случае линеаризирующая обратная связь образуется триггером Тг, вентилем В і и фильтром из элементов RiCbRaCs. Импульсы постоянной длителыюсти формируются триггером Тр, частота повторення этих импульсов зависит от работы младших разрядов счетчика Сч2 и в конечном, счете определяется частотой срабатывания сравнивающего устройства. Последняя пропорциональна преобразуемому аналоговому сигналу. Коэффициент деления импульсов эталонной частоты в счетчике Счі и импульсов выходной частоты в счетчике Сч2 одинаков.

Следует отметить, что инерционность фильтра в цепи обратной отрицательной связи ограничивает динамические возможности преобразователя. Если сглаживание импульсов осуществляется простейшим однозвенным #С-фильтром (что наименее благоприятно с точки зрения быстродействия), то время установления частоты на выходе

сравнивающего устройства до уровня 0,999 от установившегося значения при подаче скачка напряжения на вход преобразователя составит 6,9RC. В то же время, чем выше частота повторения сглаживаемых импульсов, тем меньшей может быть выбрана постоянная времени фильтра. Однако повышению частоты препятствует возрастание ошибок в формирователе импульсов.

Введение ЄЩЄ ОДНОЙ ЦЄПИ обратной СВЯЗИ (элементы R5C2ReC3) позволяет в значительной мере сократить время установления (если в устройстве (рис. 35,6) время установления ~'25 мсек при точности 0,1%, то в устройстве (рис. 35,в) при тех же условиях время установления ~200 мксек). Частота повторения импульсов, поступающих в эту цепь с выхода формирователя компенсирующих импульсов эталонной вольт-секундной площади (в данном случае это управляемый переключатель, коммутирующий источник эталонного напряжения), в k раз больше частоты импульсов цепи с фильтром R^kR%Cb.

Вопросы компенсации запаздывания (уменьшения времени установления) в импульсных следящих системах путем введения различных корректирующих цепей и выбор параметров этих цепей подробно рассмотрен в [Л. 57].

Верхняя граница диапазона преобразуемых кодирующим устройством типа аналог — частота — код величин ограничена допустимой величиной погрешностей, возникающих в аналоговых узлах, и сложностью технического выполнения цифровой части преобразователя из-за высоких частот, на которых должны работать эти элементы. Следствием этих ограничений является уменьшение крутизны характеристики вход — выход преобразователя. Однако в этом случае снижается разрешающая способность.

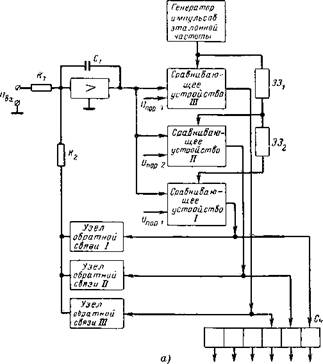

Можно расширить динамический диапазон преобразователя, разбив его на несколько поддиапазонов и изменяя крутизну характеристики вход — выход от одного поддиапазона к другому. В этом случае устройство [Л. 58] будет иметь п сравнивающих устройств и п узлов обратной связи, где п — количество поддиапазонов преобразования. Каждое из сравнивающих устройств имеет свой пороговый уровень (/пор і при срабатывании запускает соответствующий узел обратной связи, формирующий импульс эталонной вольт - секундной площади причем

Удобно / выбирать кратным разрядности счетчика преобразователя, тогда выходы соответствующих сравнивающих устройств непосредственно соединяются со входами соответствующих разрядов счетчика. В пределах каждого поддиапазона крутизна характеристики вход — выход преобразователя остается постоянной и ее величина выбирается исходя из допустимой погрешности и возможностей технического выполнения аналоговой и цифровой частей преобразователя.

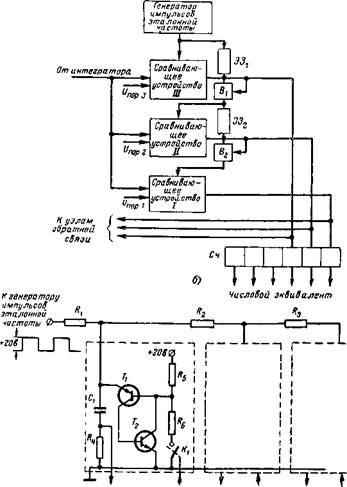

На рис. 36,а показан вариант устройства при п—3 и /=10 и, если пороговый уровень сравнивающего устройства / и вольт-се - кундную площадь импульса узла обратной связи I принять условно за 1, то пороговый уровень сравнивающих устройств II и III и вольт-секупдные площади импульсов, формируемых узлами II и III, будут соответственно 10 и 100. Управляемым параметром (дискретно изменяющимся) в узлах обратной связи является длительность формируемого импульса.

Генератор эталонных импульсов последовательно опрашивает сравнивающие устройства, начиная со старшего, в данном случае ///. Если в течение опроса сработало, например, сравнивающее устройство III (f/вых. инт^порз), импульс с выхода этого сравнивающего устройства запускает узел III, формирующий компенсирующий импульс, возвращающий интегратор в исходное состояние, и поступает в старшие разряды счетчика Сч (разряд сотен).

Если выходное напряжение интегратора в течение опроса сравнивающего устройства III меньше f/пор з и оно не сработало, происходит опрос сравнивающего устройства II и т. д.

Таким образом, в зависимости от уровня преобразуемой аналоговой величины происходит срабатывание одного из п сравнивающих устройств и соответствующего ему узла обратной связи.

Как видно, очень важное значение в работе устройства приобретает временная задержка между поступлением опросных импульсов на сравнивающие устройства. Для этого служат элементы задержки ЭЗі и ЭЗч, время задержки каждого из которых должно

|

Числовой зквиВчлянт |

быть достаточным, чтобы выходнбе напряжение HHterpaTopa ycf&- новилось до прихода на сравнивающие устройства нового импульса опроса. Для повышения надежности срабатывания сравнивающих устройств приходится либо увеличивать время задержки, либо уменьшать длительность компенсирующего импульса.

|

К узлу обратной От чубстбитель - сбязи ІП ного элемента и счетчику срабнибающего устройстбаДГ |

|

о |

Разрешением этого противоречия является введение в логику блока сравнивающих устройств вентилей В і и £2 (рис. 36,6). В этом

случае При срабатьіваїїии, например, срабниваюіцего устройства /// (U вы х. инт^^пор з)» помимо запуска узла обратной связи ///, выходным сигналом сравнивающего устройства закрывается вентиль Вь в результате чего сигнал опроса не поступает в цепи сравнивающих устройств II и I, чем предупреждается их срабатывание, даже если выходное напряжение интегратора превышает 110 или 111 условных единиц. Точно также работает вентиль В2.

В заключение приведем возможный вариант выполнения сравнивающих устройств (рис. 36,в).

Импульсы опроса от генератора эталонных импульсов амплитудной +20 в через резистор Ri заряжают конденсатор Ct. Если ключ Ки управляемый чувствительным элементом сравнивающего устройства, имеющим пороговый уровень f/пор і (например, триггер Шмитта), разомкнут, потенциал на базе транзистора Ті (в данном случае +20 в) удерживает его в запертом состоянии, в результате чего и транзистор Т2 находится также в запертом состоянии.

Срабатывание чувствительного элемента приводит к замыканию ключа /Сь потенциал на базе Ті становится равным +10 в. Устройство готово к работе, и при поступлении на него очередного импульса опроса начинается регенеративный процесс, приводящий к переходу транзисторов 7 и Т2 в открытое состояние. Конденсатор Сі разряжается, что приводит к появлению на резисторе /?4 скачка напряжения, передним фронтом которого запускается соответствующий узел обратной связи и соответствующий разряд счетчика импульсов.

В течение действия импульса опроса эмиттерный ток транзистора Ті остается достаточным для поддержания его и транзистора Г2 в открытом до насыщения состоянии.

Постоянные времени заряда конденсатора Сі в соответствующих сравнивающих устройствах I, II, III выбраны таким образом, что при сработавших чувствительных элементах этих устройств и при замкнутых ключах /Сі конденсаторы Сі в сравнивающих устройствах // и / при опросе сравнивающего устройства III начнут разряжаться раньше, чем напряжение на этих конденсаторах достигнет уровня открывания транзистора 7t и Т2 сравнивающих устройств II и I. Тем самым блокируется действие устройств II и I при работе сравнивающего устройства III.

Наоборот, если чувствительный элемент сравнивающего устройства III не сработал (£/Вых. ипт<£/пор з) и ключ Ki разомкнут, напряжение на конденсаторе Ct заряжаемом в течение целого цикла импульсов опроса, не достигнет напряжения открывания транзистора Ті. Последний совместно с транзистором Т2 останется в исходном состоянии. Сравнивающее устройство III не будет влиять на работу преобразователя.

Подобным образом работают остальные устройства сравнения.